Home /

Expert Answers /

Electrical Engineering /

w-the-circuit-shown-in-the-figure-uses-a-3-8-decoder-implemented-using-two-2-4-decoders-and-an-in-pa414

(Solved): W The circuit shown in the Figure uses a 3:8 decoder (implemented using two 2:4 decoders and an in ...

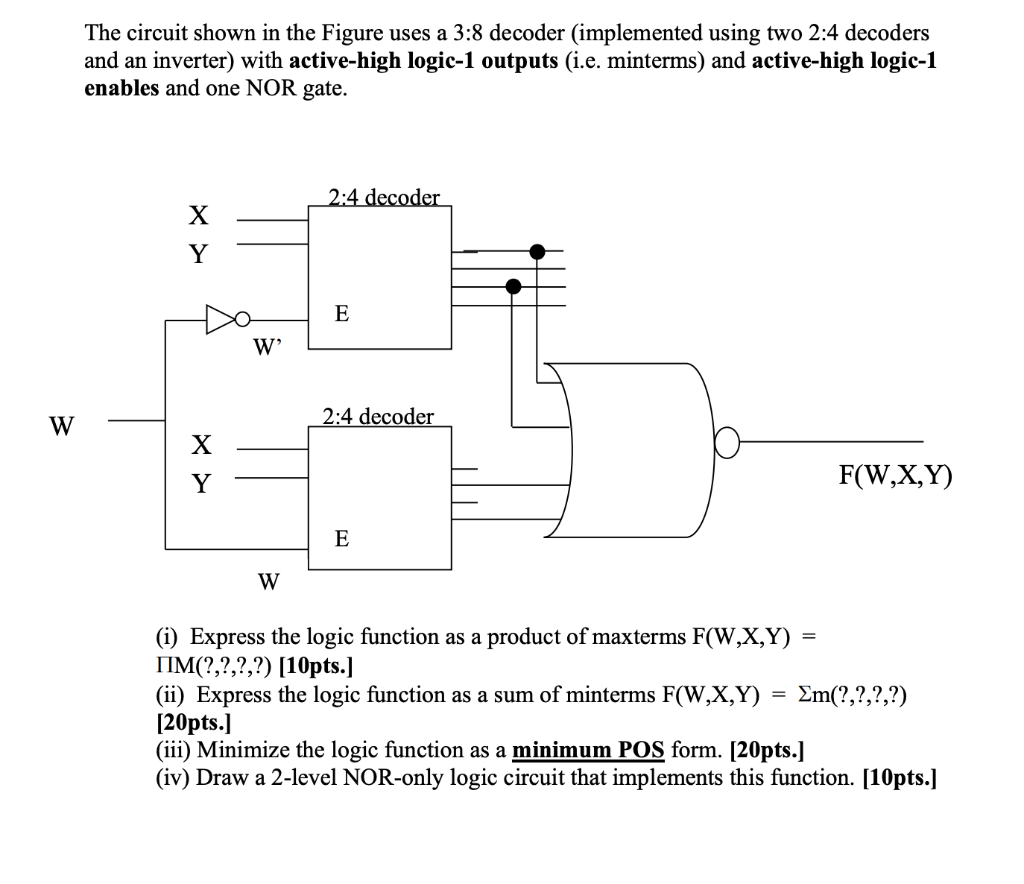

W The circuit shown in the Figure uses a 3:8 decoder (implemented using two 2:4 decoders and an inverter) with active-high logic-1 outputs (i.e. minterms) and active-high logic-1 enables and one NOR gate. X Y X Y W' W 2:4 decoder E 2:4 decoder E F(W,X,Y) (i) Express the logic function as a product of maxterms F(W,X,Y) TIM(?,?,?,?) [10pts.] (ii) Express the logic function as a sum of minterms F(W,X,Y) [20pts.] (iii) Minimize the logic function as a minimum POS form. [20pts.] (iv) Draw a 2-level NOR-only logic circuit that implements this function. [10pts.] = Em(?,?,?,?)