Home /

Expert Answers /

Electrical Engineering /

using-vhdl-language-altera-quartus-20-1-software-and-terasic-de10-lite-board-you-should-des-pa268

(Solved): Using VHDL language, ALTERA Quartus \( 20.1 \) software and Terasic DE10-Lite board, you should des ...

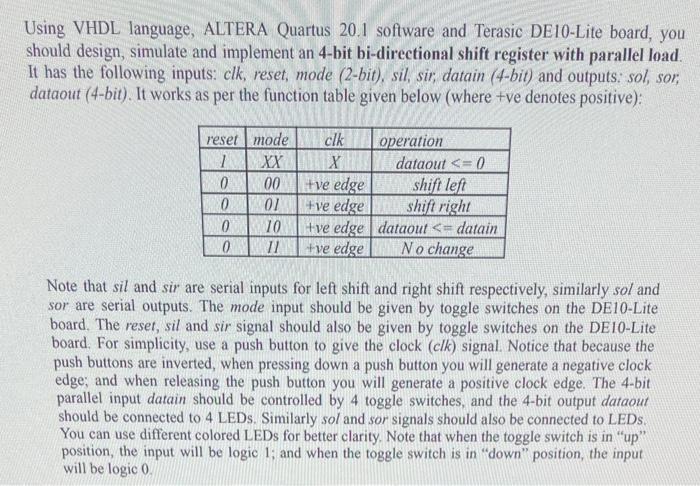

Using VHDL language, ALTERA Quartus \( 20.1 \) software and Terasic DE10-Lite board, you should design, simulate and implement an 4-bit bi-directional shift register with parallel load. It has the following inputs: clk, reset, mode (2-bit), sil, sir, datain (4-bit) and outputs: sol, sor; dataout (4-bit). It works as per the function table given below (where +ve denotes positive): Note that sil and sir are serial inputs for left shift and right shift respectively, similarly sol and sor are serial outputs. The mode input should be given by toggle switches on the DE10-Lite board. The reset, sil and sir signal should also be given by toggle switches on the DE10-Lite board. For simplicity, use a push button to give the clock (clk) signal. Notice that because the push buttons are inverted, when pressing down a push button you will generate a negative clock edge; and when releasing the push button you will generate a positive clock edge. The 4-bit parallel input datain should be controlled by 4 toggle switches, and the 4-bit output dataout should be connected to 4 LEDs. Similarly sol and sor signals should also be connected to LEDs. You can use different colored LEDs for better clarity. Note that when the toggle switch is in "up" position, the input will be logic 1 ; and when the toggle switch is in "down" position, the input will be logic 0 .

Expert Answer

ANSWER:- --VHDL Code library ieee; use ieee.std_logic_1164.all; entity shift_reg is port ( clk : in std_logic; reset : in std_logic; mode : in std_log