Home /

Expert Answers /

Computer Science /

draw-a-pipeline-diagram-illustrating-how-the-following-assembly-sequence-would-execute-on-a-fully-b-pa774

(Solved): Draw a pipeline diagram illustrating how the following assembly sequence would execute on a fully b ...

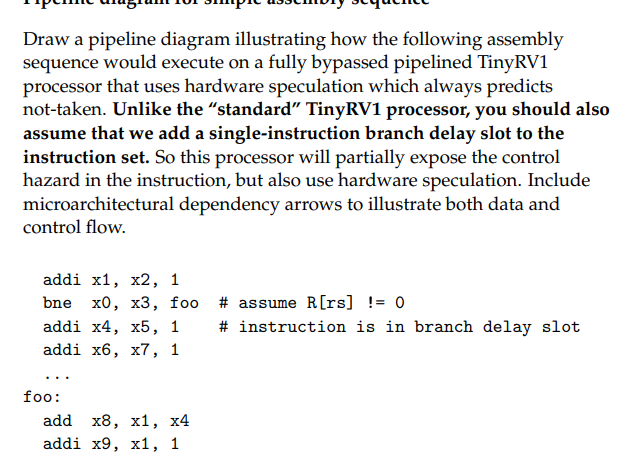

Draw a pipeline diagram illustrating how the following assembly sequence would execute on a fully bypassed pipelined TinyRV1 processor that uses hardware speculation which always predicts not-taken. Unlike the "standard" TinyRV1 processor, you should also assume that we add a single-instruction branch delay slot to the instruction set. So this processor will partially expose the control hazard in the instruction, but also use hardware speculation. Include microarchitectural dependency arrows to illustrate both data and control flow. addi bne , foo \# assume addi \# instruction is in branch delay slot addi . add addi addi bne , foo \# assume addi \# instruction is in branch delay slot addi ... foo: add addi