Home /

Expert Answers /

Electrical Engineering /

2-cpi-calculation-a-processor-has-the-following-specs-system-clock-200-mathrm-mhz-m-pa787

(Solved): 2. CPI Calculation A processor has the following specs: System Clock: \( 200 \mathrm{MHz} \) \( \m ...

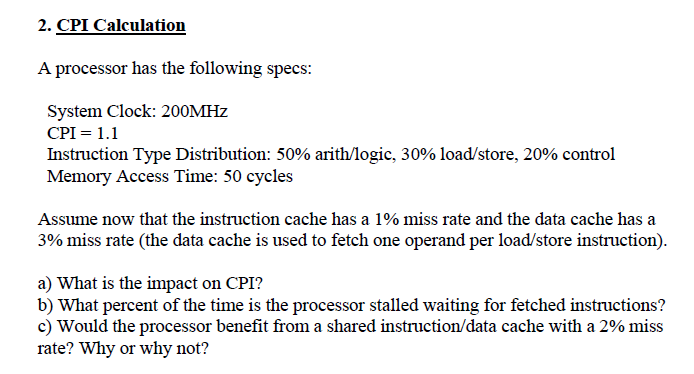

2. CPI Calculation A processor has the following specs: System Clock: \( 200 \mathrm{MHz} \) \( \mathrm{CPI}=1.1 \) Instruction Type Distribution: \( 50 \% \) arith/logic, \( 30 \% \) load/store, \( 20 \% \) control Memory Access Time: 50 cycles Assume now that the instruction cache has a \( 1 \% \) miss rate and the data cache has a \( 3 \% \) miss rate (the data cache is used to fetch one operand per load/store instruction). a) What is the impact on CPI? b) What percent of the time is the processor stalled waiting for fetched instructions? c) Would the processor benefit from a shared instruction/data cache with a \( 2 \% \) miss rate? Why or why not?